Daily Briefing: News Snippets

# EMBEDDED SYSTEMS VOLUME 7 NUMBER 1 JAN/FEB 12011

INCLUDING.

Chris A. Ciufo

Warfighters need portable power

Field Intelligence

Mezzanines continue to evolve

Mil Tech Insider

Digital-video open standards drive infrastructure

**Legacy Software Migration**

Objective Interface Systems:

Legacy middleware meets multicore environments

MIL-EMBEDDED.COM

## Intel's inside ... everything

**CPU does Windows, DSP, and UAS/UAVs**

www.opensystemsmedia

SUBSCRIBE

mil-embedded.com/subscribe

#### That's the nature of the AB2000 Avionics BusBox®

With so many built-in capabilities, the highly-flexible AB2000 family from Ballard Technology is the ideal fit for a wide range of applications. These rugged, conduction-cooled, COTS devices combine a powerful computer processor, multi-protocol databus interfaces, Ethernet, USB, other I/O, and PMC expansion in a small, lightweight package.

#### Discover what the AB2000 can do for you.

Call 425.339.0281 or email sales@ballardtech.com today.

The Avionics Databus Innovators AS9100 / ISO 9001 Registered

#### AB2000 Personalities...

- · Embedded Computer

- · Aircraft Interface Device

- · Data Recorder

- · Protocol Converter

- · Ethernet Switch

- · Power Management Unit

- · Radio/Satcom Interface

- · and many more

www.ballardtech.com/AB2000

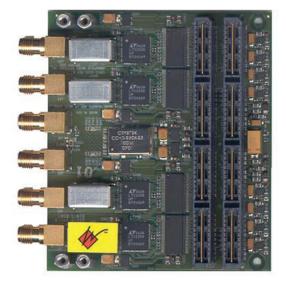

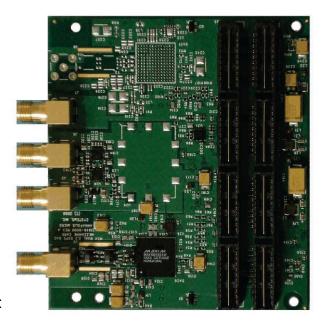

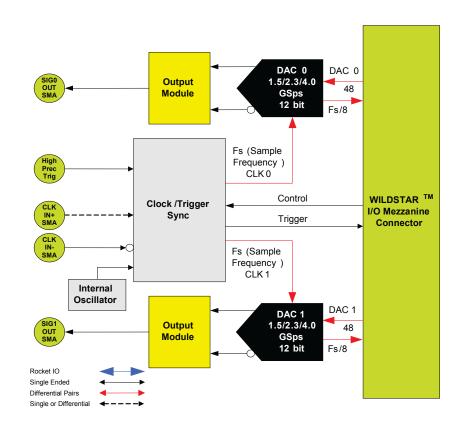

#### Annapolis Micro Systems

The FPGA Systems Performance Leader

### High Performance Signal and Data Processing in Scalable FPGA Computing Fabric

GEOINT, Ground Stations, SDR, Radar, Sigint, COMINT, ELINT, DSP, Network Analysis, Encryption, Image Processing, Pattern Matching, Oil & Gas Exploration, Financial Algorithms, Genomic Algorithms

Direct Seamless Connections with no Data Reduction Between External Sensors and FPGAs Between FPGAs and Processors over IB or 10GE Between FPGAs and Standard Output Modules Between FPGAs and Storage Arrays

Ultimate Modularity

From 1 to 8 Virtex 4, 5 or 6 FPGA/Memory Modules

Input/Output Modules Include:

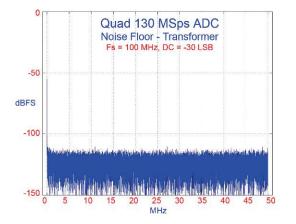

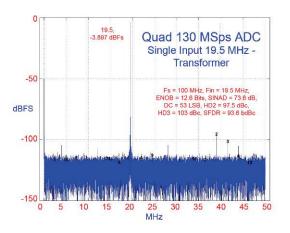

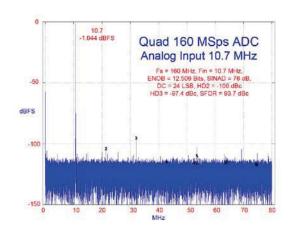

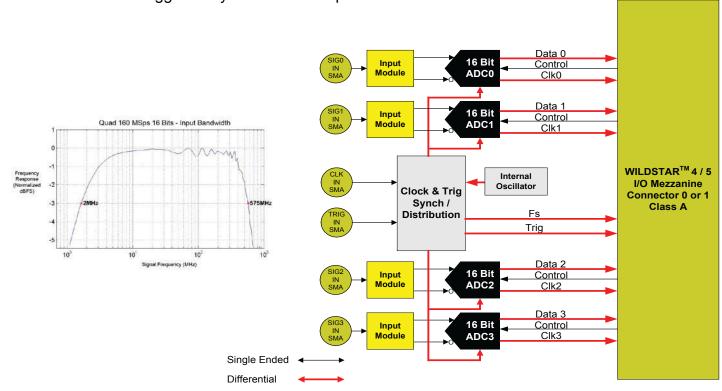

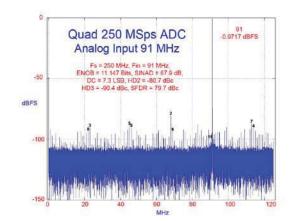

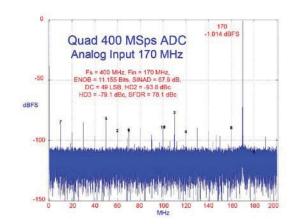

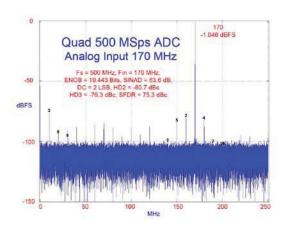

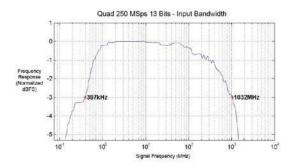

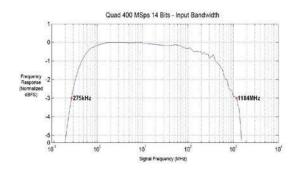

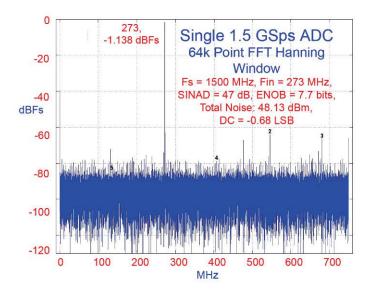

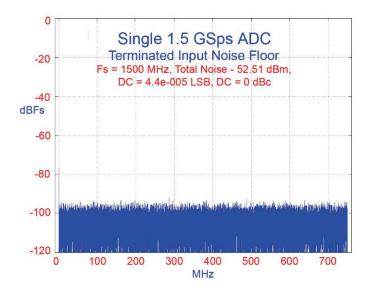

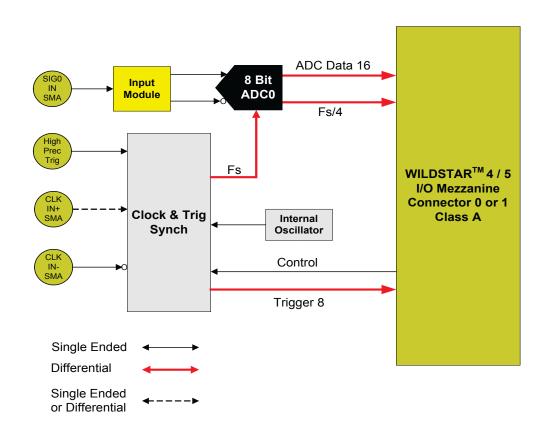

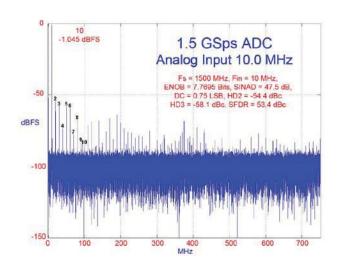

Quad 130 MSPS thru Quad 550 MSPS A/D

1.5 GSps thru 5.0 GSps A/D, Quad 600 MSps D/A,

Dual 1.5 GSps thru 4.0 GSps D/A

Infiniband, 10G, 40G or 100G Ethernet or SFPDP

VME/VXS/VPX, IBM Blade, PCI-X/PCI Express, PMC/XMC, MicroTCA

No Other FPGA Board Vendor Streams This Volume of Data Real Time Straight Into the Heart of the Processing Elements and Then Straight Back Out Again

190 Admiral Cochrane Drive, Suite 130, Annapolis, Maryland USA 21401 wfinfo@annapmicro.com USA (410) 841-2514 www.annapmicro.com

# EMBEDDED SYSTE

January/February 2011 Volume 7 Number 1

#### **COLUMNS**

#### Field Intelligence

Mezzanines continue to evolve By Duncan Young

#### Mil Tech Insider

Open standards for digital video drive common infrastructure

By Steve Edwards

#### **Legacy Software Migration**

Migrating legacy middleware to multicore environments

By Charles Rush, Objective Interface Systems, Inc.

#### **Crosshairs Editorial**

42 "For want of a nail, the shoe was lost." Forget about shoes; warfighters need portable power By Chris A. Ciufo

#### **DEPARTMENTS**

16-17 **Daily Briefing: News Snippets** By Sharon Hess

40-41 Editor's Choice Products

#### ON THE COVER:

Increasingly, UAS payloads like those of this MQ-9 Reaper capture more video, include more sensors, and are prime candidates to let Intel Core processors crunch DSP algorithms. See article on page 26. Photo provided by General Atomics Aeronautical Systems, Inc.

ISSN: Print 1557-3222

All registered brands and trademarks within Military Embedded Systems magazine are the property of their respective owners.

© 2011 OpenSystems Media © 2011 Military Embedded Systems

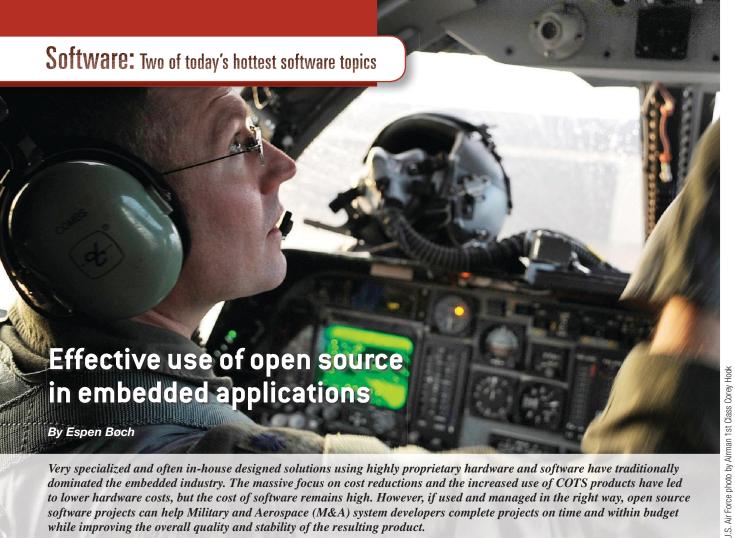

#### Software: Two of today's hottest software topics

18 Enhancing application performance on multicore systems

By John Blevins, LynuxWorks

22 Effective use of open source in embedded applications

By Espen Bøch, Galleon Embedded Computing

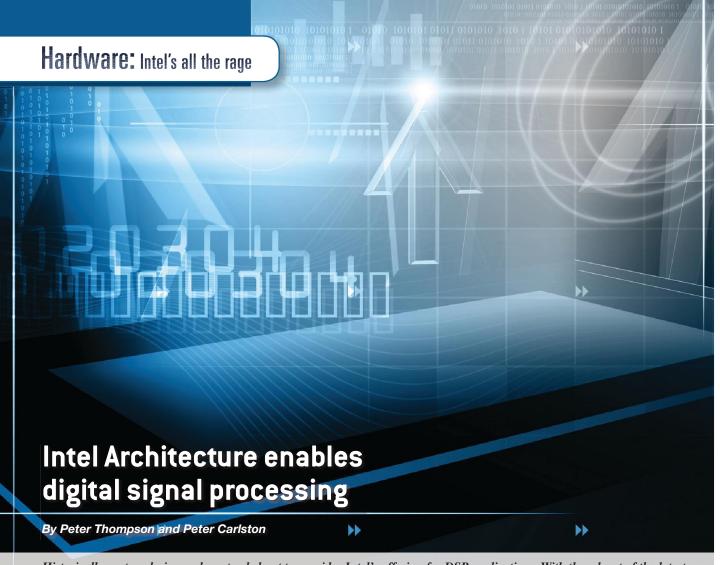

#### Hardware: Intel's all the rage

Intel Architecture enables digital signal processing 26

By Peter Thompson, GE Intelligent Platforms and Peter Carlston, Intel Corporation

#### Technology: Predictions

2011: Top technologies for the warfighter 30 By Chris A. Ciufo

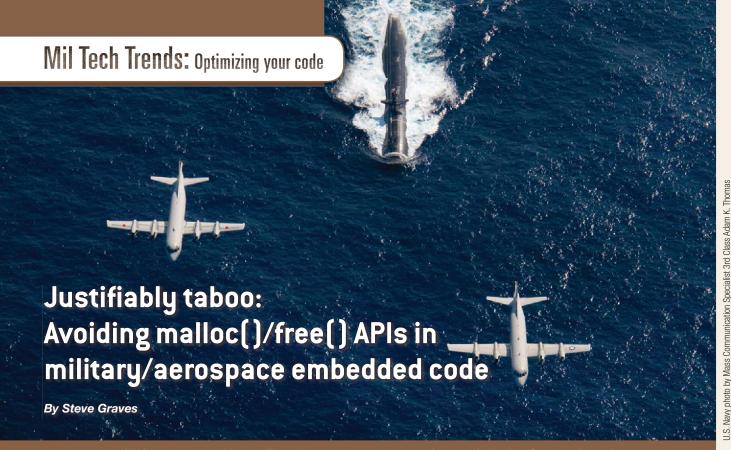

#### Mil Tech Trends: Optimizing your code

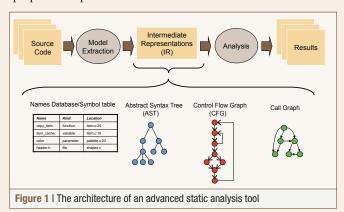

Domain-specific property checking with 32 advanced static analysis

By Paul Anderson, GrammaTech, Inc.

Justifiably taboo: Avoiding malloc()/free() APIs in military/aerospace embedded code

By Steve Graves, McObject

#### **EVENTS**

http://events.opensystemsmedia.com

#### **Embedded World 2011**

March 1-3, 2011 • Nürnberg, Germany www.embedded-world.eu

#### ESC Silicon Valley

May 2-5, 2011 • San Jose, CA http://esc-sv09.techinsightsevents.com

#### E-CAST

http://ecast.opensystemsmedia.com

Simplifying the Complexities of Multicore Processors with COTS Single Board Computer Solutions

February 17, 2011 • 12pm MST Presented by: Freescale Semiconductor, Emerson Network Power, Eurotech Inc.

#### **WEB RESOURCES**

Subscribe to the magazine or E-letter Live industry news • Submit new products

http://submit.opensystemsmedia.com

#### White papers:

Read: http://whitepapers.opensystemsmedia.com Submit: http://submit.opensystemsmedia.com

#### » Where can I find a single source for my embedded computing project? «

Kontron is your single source for COTS products and specialized systems designs built to meet the most demanding requirements.

#### CRITICAL QUESTIONS ... ANSWERED

#### VX6060

6U VPX Dual Intel® Core™ i7 Single Board Computer

- » Available in air-cooled & conduction-cooled versions

- » Compliant to VITA46(VPX), VITA65 (OpenVPX) and VITA48 (VPX REDI)

#### Kontron EAPI

Kontron Embedded Application **Programming Interface**

- » Unified middleware for access & control of hardware

- » Includes standard libraries & APTS

#### **Cobalt™**

Reduced SWAP - High Performance Embedded Computer

- » Small Form Factor

- » Intel® Core™2 Duo or Atom™ processor options

- » Custom I/O option

**1-888-294-4558**

☑ info@us.kontron.com

@www.kontron.com/military

| ADVERTISER INFORMATION |                                                                                        |

|------------------------|----------------------------------------------------------------------------------------|

| Page                   | Advertiser/Ad title                                                                    |

| 3                      | Annapolis Micro Systems, Inc. –<br>High performance signal and data<br>processing      |

| 2                      | <b>Ballard Technology</b> – A surprising blend of personalities                        |

| 27                     | CoreSolid Storage – XDOM mini<br>PCI Express DiskOnModule                              |

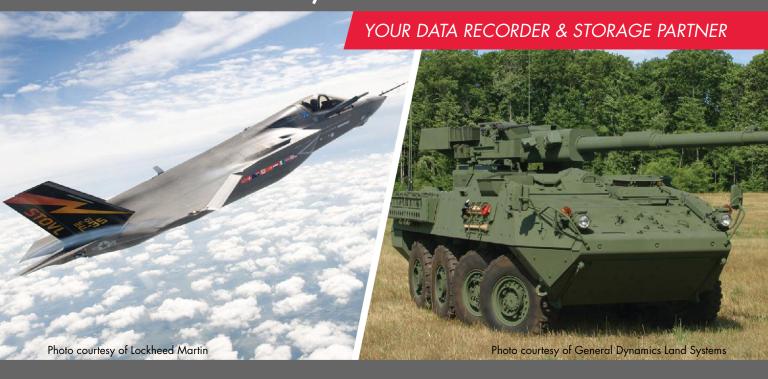

| 44                     | Curtiss-Wright Controls Electronic<br>Systems – Rugged, secure data<br>storage         |

| 35                     | <b>D-TA Systems</b> – 10G series record & playback systems                             |

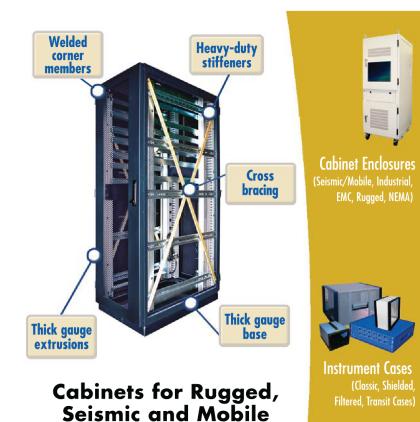

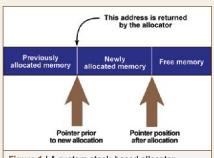

| 28                     | Elma Electronic – Cabinets for rugged, seismic and mobile applications                 |

| 37                     | Elma Electronic – Systems –<br>Embedded storage for secure data                        |

| 15                     | Excalibur Systems, Inc. – Dragon                                                       |

| 25                     | Extreme Engineering Solutions –<br>2nd generation Intel Core i7 processor<br>solutions |

| 29                     | Galleon Embedded Computing –<br>Setting new standards for rugged<br>storage            |

| 43                     | <b>GE Intelligent Platforms, Inc.</b> – From proposal to deployment in record time     |

| 7                      | Hypertronics – Discover                                                                |

| 5                      | Kontron – Where can I find a single source for my embedded computing project?          |

| 38                     | <b>Kontron</b> – VX6060 - 6U VPX dual<br>Intel Core i7 single board computer           |

| 14                     | Microhard Systems, Inc. –<br>Wireless innovation                                       |

| 10                     | Microsemi – We create space                                                            |

| 20                     | Nallatech – One stop SWaP                                                              |

| 39                     | Pentek, Inc. – Stroke of genius                                                        |

| 34                     | Phoenix International – RPC12<br>ruggedized 3U Fibre Channel<br>RAID system            |

| 9                      | RTD Embedded Technologies, Inc. –<br>Modularity at its best                            |

| 24                     | Themis Computer – Mission and payload systems                                          |

| 33                     | VersaLogic Corp. – Extreme                                                             |

#### WWW.MIL-EMBEDDED.COM

embedded performance

Wind River Aerospace & Defense **Division** - Mission critical

WinSystems, Inc. – 1 GHz PC/104

SBC supports networking and

**DSP-FPGA.com**

#### Military & Aerospace Group

Chris Ciufo, Group Editorial Director cciufo@opensystemsmedia.com

Sharon Hess, Assistant Managing Editor sharon\_hess@opensystemsmedia.com

Jennifer Hesse, Assistant Managing Editor jhesse@opensystemsmedia.com

Terri Thorson, Senior Editor (columns) tthorson@opensystemsmedia.com

Monique DeVoe, Web Content Editor mdevoe@opensystemsmedia.com

Christine Capuano, Web/Editorial Assistant

Hermann Strass, European Representative hstrass@opensystemsmedia.com

Konrad Witte, Senior Web Developer

Steph Sweet, Creative Director

Joann Toth, Senior Designer

David Diomede, Art Director

Matt Jones, Web Developer

Phyllis Thompson

Circulation/Office Manager subscriptions@open systems media.com

#### Sales Group

Dennis Doyle, Senior Account Manager ddoyle@opensystemsmedia.com

Tom Varcie, Senior Account Manager tvarcie@opensystemsmedia.com

#### Rebecca Barker

Strategic Account Manager rbarker@opensystemsmedia.com

#### **Christine Long**

Digital Content Manager clong@opensystemsmedia.com

#### **International Sales**

#### Elvi Lee

Account Manager - Asia elvi@aceforum.com.tw

#### Regional Sales Managers

Barbara Quinlan, Midwest/Southwest bquinlan@opensystemsmedia.com

Denis Seger, Southern California dseger@opensystemsmedia.com

Sydele Starr, Northern California sstarr@opensystemsmedia.com

Ron Taylor, East Coast/Mid Atlantic rtaylor@opensystemsmedia.com

#### **Ad Coordinator**

#### Steph Sweet

ssweet@opensystemsmedia.com

#### **Reprints and PDFs**

#### Nan Holliday

800-259-0470

republish@opensystemsmedia.com

#### **Editorial/Business Office**

16626 E. Avenue of the Fountains, Ste. 203 Fountain Hills, AZ 85268

Tel: 480-967-5581 ■ Fax: 480-837-6466 Website: www.opensystemsmedia.com

Publishers: John Black, Michael Hopper, Wayne Kristoff

Vice President Editorial: Rosemary Kristoff

Vice President Marketing & Sales:

Patrick Hopper

phopper@opensystemsmedia.com

Business Manager: Karen Layman

21

13

communications

#### NEW LEVELS OF INTERCONNECT RELIABILITY

For lengthy space missions tasked with discovering the effects of atmospheric phenomena on vital communication transmissions and data gathering, it's critical that equipment be long lasting and impervious to damaging effects. Hypertronics interconnect solutions featuring the Hypertac® hyperboloid contact technology offer the reliability and dependability that are required in making space discovery possible. Hypertronics is the choice of engineers worldwide for mission critical systems.

#### **Hypertac Features**

Low Insertion/Extraction Forces Long Contact Life Lower Contact Resistance Higher Current Ratings Shock and Vibration Immunity

#### Benefits

High Density Interconnect Systems Low Cost of Ownership Low Power Consumption Maximum Contact Performance Reliability Under Harsh Conditions

Maintain your system integrity with Hypertronics reliable connectors and dependable solutions.

www.hypertronics.com/discover

HYPERTRONICS: WHEN FAILURE IS NOT AN OPTION

#### Field Intelligence

#### **Mezzanines** continue to evolve

The ability to customize the functionality of off-the-shelf embedded computing modules by the addition of mezzanines has become an essential element in the battle to get the most from the least space at an affordable price. Mezzanine standards abound, one of the most common being "IEEE1386.1, PMC/XMC," which can be used with many types of architectures such as VMEbus, VPX (VITA 46), and CompactPCI, as well as the desktop PC using PCI carrier cards.

The PMC standard was introduced more than 15 years ago and offers an ideal amount of real estate. It has been continuously improved with greater connectivity, an extended PCI bus, better power dissipation and, most recently, support for high-speed serial signaling such as PCI Express between mezzanine and base card. Continuous improvement has yielded a quadrupling of the PMC's power dissipation capability compared to the original IEEE1386.1 specification, as more functionality and performance get packed into its limited space.

#### **PMC** applications

There are many different military applications for PMC modules, ranging from flash storage, avionics bus interfaces, and general-purpose I/O, to Network Interface Controllers (NICs) and switches to sensor processors. Some of the most challenging of these PMC applications are sensor front-end processors using either an FPGA or the emerging GPGPU-based processing arrays. Using these types of devices pushes the boundaries of power dissipation. Typically, such a sensor processing PMC incorporating, for example, a Xilinx Virtex-5 FPGA and high-speed analog I/O will dissipate almost 30 W. These types of front-end processors are often used as digital downconverters, video processors, or radar pre-processors. With the addition of analog O/P, a complete Electronic Support Measures (ESM) subsystem can be configured on a single PMC module, in many cases able to operate without runtime processor intervention.

#### Multiple PMC/XMC modules

Because PMC/XMC modules offer such efficient use of space, subsystems often get configured with more mezzanine modules than can be fitted to just one SBC. A 3U-sized SBC is limited to one mezzanine slot, whereas 6U accommodates two. Carrier cards provide the means of adding further mezzanine slots within a chassis, but must be connected to the SBC via PCI, PCI-X, or PCI Express, generally using the SBC's PMC/XMC site to make this connection. In a VPX environment, adding further XMC modules has been simplified. They can be plugged directly onto a passive carrier card into any backplane slot supporting PCI Express. However, where PCI Express is not so readily available, other configurations and permutations might require PCI bridges, for example, to support a PCI Express mezzanine in a PCI-X environment.

The myriad embedded products vendors supporting PMC/XMC mezzanines recognize the ways that the original specification has been stretched to accommodate today's levels of performance and functionality. This is reflected in their SBC designs, which account for the additional power needs and provide well-managed signal routing and noise containment through the use of best practices. This is not always the case in the prototyping laboratory where critical PMC/XMC modules might be incorporated into a desktop PC environment using a PCI carrier.

Compared to a rack-mounted modular system, a desktop's PCI and PCI-X slots can be electrically noisy and lack sufficient power or heat management to support leading-edge PMC/XMC modules. In this case, the PCI carrier card can be vital to remedying these shortcomings. One viable example of this is the soon-to-be-announced short form factor PCI Express carrier card from GE Intelligent Platforms (Figure 1) supporting Gen2 x8 PCI Express to the host and including cooling for high-power PMC or XMC modules.

Figure 1 | Short form factor PMC carrier card for PCI applications from GE Intelligent Platforms

#### New mezzanine proposals

Just as VPX provides a step increase in capability compared to its VMEbus forebear, significant evolution of mezzanine standards will be needed to maintain future technology leadership. A VITA 71/ Rugged Mezzanine working group has been formed to evaluate and create standards for a new generation of mezzanines for embedded computing users. Based on the considerable industry experience gained with the PMC/XMC standards, significant advances can be expected:

- Increased interoperability among

- Improved connectors with signaling rates to 12 GHz

- More efficient space utilization by reducing connector sizes and keep-out areas

- Fewer power rails

- Greater power dissipation

- A wider range of sizes

The standardization of mezzanine specifications will continue to be challenging as SBC designers need to anticipate a multiplicity of mezzanine vendors plus future growth in capability and performance. The result can be overspecification or the provision of many unused resources to meet every eventuality. VITA 71 needs to address these issues to level the playing field, yet at the same time leaving scope for the continued innovation and evolution so essential to a standard's long-term future.

To learn more, e-mail Duncan at duncan\_young1@sky.com.

#### RTD Embedded Technologies, Inc.

Modularity at its Best.

Above: PCI/104-Express Intel® Core™ 2 Duo IDAN® showing how easy it is to upgrade, repair or re-configure RTD's modular, rugged systems based on mission requirements.

Easy Upgrade

New Functionality

the industry in PCI/104-Express offering. RTD proudly leads

**The Leading Source for PCI Express**

Design, Engineering, Manufacturing & Tech Support

Microsemi's microelectronic solutions increase board density, reduce design complexity, and extend product life and environmental performance in military applications. We offer design, assembly and test of custom multi-chip solutions, and a wide range of standard military off-the-shelf space-saving solutions.

Expand the possibilities; visit **www.whiteedc.com/spacesaving.**

Our 8Gb DDR3 SDRAM is the first true x72 DIMM in a single BGA package. The 128Mx72 SDRAM is available in a 375 PBGA, saving 30% space and providing a 21% I/O reduction over a comparable discrete configuration. With data rates of 800, 1066 and 1333 Mb/s, it operates on a 1.5 volt power supply. This high-reliability extended temp SDRAM is designed for mission-critical applications in military and aerospace equipment.

With densities up to 4GByte in 512Mx72 and 512Mx64 configurations, the Microsemi DDR3 family provides many benefits, such as: space savings; reduced I/O routing; superior signal integrity; reduced component count and placements; and extended temperature range testing, including industrial and military.

Learn more at www.whiteedc.com/ddr3\_sdram.html

Securing the Future Through the Power of Design 602.437.1520 TEL | 602.437.9120 FAX

W W W . W H I T E E D C . C O M

#### Mil Tech Insider

#### Open standards for digital video drive common infrastructure

By Steve Edwards

The complexity of deployed embedded military systems increases as more video sensors are added to ground and airborne platforms, delivering ever-increasing amounts of video data to be processed, viewed, and archived. As the variety of video sensors used in military radar and signal processing applications continues to multiply, many of which feature incompatible input requirements, the result has been increased system complexity. One key area of complexity is the cabling and configuration needed to distribute multispectral data within these sensor-to-video/-display/-recorder embedded systems.

Today's military platforms often have upwards of dozens of sensors, making the real-time distribution of video data a real challenge. The good news is that open standards are underway and gaining traction, such as the new DEFSTAN 00-82 standard in the UK. This trend is helping to drive industry use of standard media, such as 10 GbE to transport data, which will reduce system complexity and promote system interoperability.

#### The open standards approach

A standard approach to digital video connectivity will help military suppliers provide compatible subsystems that support a common infrastructure. Emerging standards for digital video interoperability support this approach. One example, as mentioned, is a well advanced, recently published standard in the UK: DEF STAN 00-82, which establishes protocols for video digital streaming. This standard is being mandated by the UK Ministry of Defence's (MoD's) Generic Vehicle Architecture standard (DEF STAN 23-09), which is overseen by a standards consortium. Curtiss-Wright Controls Embedded Computing (CWCEC) recently demonstrated implementations of digital video streaming and recording over a 10 GbE fabric using DEF STAN 00-82.

A typical video distribution system architecture comprises the front-end interfaces to the sensors, which accept data from legacy analog systems (RGB or composite video) and newer interfaces such as HD-SDI and 3G-SDI. It can also accept streamed video data from networkcompatible sensors that generate data onto a digital network, such as GbE Vision, or systems built on top of Real-time Transport Protocol (RTP), as invoked by DEF STAN 00-82. Multiple video streams are then sent through a rugged Ethernet switch and multiplexed to create the 10 GbE fabric of the video network within the platform.

The platform's video processing and data storage equipment, such as CWCEC's Sentric2 digital video recorder, connect to the 10 GbE fabric to extract multiple video feeds from the multiplexed stream (Figure 1). The appropriate image processing can then be performed on the video data, such as multispectral image fusion, image registration and stabilization, image enhancement, and image stitching that combines multiple sensor views to provide an outside view of the platform.

Figure 1 | The Sentric2 High-Definition Video Recorder System captures, compresses, and stores multiple channels of high-resolution analog or digital video, composite TV, network video, and audio in digital formats.

#### Supporting heterogeneous protocols

By using an open standard for transporting multispectral data over a single network, the system designer is also able to eliminate the need to translate different video protocols. The results are a unified transport medium and a unified vocabulary for controlling the various video sources and the format of the video streams.

The best advantage of using a common digital video streaming format is that it eliminates the need to perform protocol conversion, which can be costly for highbandwidth video data. A better method is for the sensor to speak the same language as the equipment receiving the video signal. There are two aspects to video protocols: data and control. It is especially important that the equipment that wants to subscribe to video streams from specific sensors be able to speak a control language that those sensors understand. The control language should be sufficiently generic that multiple manufacturers can conform to that standard with their own specialized equipment.

#### Eliminating dedicated cabling

Typically, individual cabling is used to connect each video sensor to the dataconcentration point. The common infrastructure approach eliminates the need for multiple cables in a confined space, supporting transmission over a standard network of HD sensor video, simultaneous digital video, and metadata recording. It also enables multiple video streams to be concentrated at one or more processing units to undergo advanced image-fusion techniques.

#### Keeping up with sensor proliferation

Attaining video sensor data interoperability with open standards and a common infrastructure network will help COTS vendors keep up with the growth of sensors on military platforms. The real-time battlefield data these sensors provide saves lives and supports critical missions. Reducing cabling and configuration complexity and providing a high-bandwidth common architecture for distributing video sensor data will enable onboard processors to take full advantage of the growing amounts of video sensor data being made available to today's warfighter.

To learn more, e-mail Steve at Steve.Edwards@curtisswright.com. 1 GHz PC/104 SBC Supports Networking and Communications

Hardened for harsh, rugged environments, the low power PCM-VDX-2 PC/104 single board computer is ideal for Mil/COTS applications. It is packed with serial, USB, and Ethernet ports, plus GPIO. With its diverse range of functions, most applications will not require additional I/O cards; however, it has Mini PCI and PC/104 connectors for specialty I/O expansion.

• Fanless, low power 1GHz Vortex86DX processor

• PC/104 Bus compliant form factor (90 x 96 mm)

512MB of soldered-down onboard DRAM

- · 1MB of battery-backed SRAM

- CompactFlash socket

- Optional 512MB onboard SSD flashdisk

- Full-featured I/O includes:

- Two 10/100 Mbps Ethernet ports

- Four USB 2.0 ports

- ESD protection on LAN, USB, and serial ports

- Four serial RS-232/422/485 ports

- 16 lines of general purpose I/O

- PATA, LPT, PS/2 KYBD and Mouse controller

- Mini PCI and PC/104 expansion connectors

- · WDT, RTC, status LEDs, and beeper

- Extended temperature -40°C to +85°C operation

- Runs Linux, DOS, and other x86-compatible operating systems

- Downloadable drivers available

- · Responsive and knowledgeable technical support

Understanding long-term product availability is a critical issue for Mil/COTS customers, the PCM-VDX-2 is offered beyond 2017.

Contact us for additional product information and pricing. Our factory application engineers look forward to working with you.

Ask about our 30-day product evaluation.

Call 817-274-7553 or Visit www.winsystems.com/PCM-VDX

715 Stadium Drive • Arlington, Texas 76011 Phone 817-274-7553 • FAX 817-548-1358 E-mail: info@winsystems.com

Multicore microprocessors in embedded defense systems are becoming ubiquitous. Embedded systems have specialized requirements, such as heat dissipation and battery life, that restrict the ability to simply crank up the clock speed of a processor. Embedded microprocessor designers grappling with these physical limitations have turned to multicore architectures as a preferred method for continuing geometric performance improvements. Multicore ARM and PowerPC chips are already available, and Intel is pushing its low-power multicore processors into embedded designs. For defense system architects updating legacy systems with new capabilities, incorporating a multicore processor can require an analysis and development effort that extends well beyond the traditional software port.

Unlike the performance increases from boosting microprocessor clock speeds, accessing the performance potential of a multicore processor often requires engineering development

Wireless Innovation ROBUST DESIGN | EXCELLENT SENSITIVITY | MAXIMUM POWER Serial USB Soð Masterless Ethernet Nano IP Series - Miniature Wireless Ethernet/Serial/USB Gateway VLAN • Airborne Repeater • AD-HOC Data Rates up to 1.2 Mbps Adjustable Output Power (1W) Miniature Size (1.25"x2"x0.5") ✓ Fully Tested From -40 to  $+85^{\circ}$ C Extremely Light (Only 24 grams!) No Additional Hardware Required! **Two Serial Interfaces Ethernet Interface USB Interface** 300 to 450MHz .35 to 1.3<u>9GHz</u> Also Available in Serial Only Model **Products Available Ranging** From 300 MHz to 5.8 GHz nard systems inc. www.microhardcorp.

efforts to a parallelize software execution. Along with efforts of identifying, expressing, and implementing parallelization, most approaches to parallel software require the explicit management of communications and shared resources. Selecting a set of software components that already addresses these concerns can greatly simplify the transition to a multicore microprocessor architecture.

In particular, the critical but invisible middleware that provides the communication framework for many embedded systems can become a significant asset in simplifying the architecture and design of a multicore system. Software engineers in pursuit of multicore performance often overlook the influence middleware has, and how the proper choice of middleware can significantly improve performance.

#### How middleware simplifies defense systems architecture

Middleware frameworks evolved to help software developers overcome the inherent complexity of programming for distributed systems. The complexity resulted from the heterogeneity of networks, hardware, operating systems, and programming languages present in many systems. The Common Object Request Broker Architecture (CORBA) is a standards-based middleware that communicates among operating systems, multiple languages (C++, Ada, and Java), microprocessors (x86, PowerPC, ARM, MIPS, and so on), and data transports (Ethernet, PCI Express, shared memory, RapidIO, InfiniBand, and so on). CORBA has been used in defense applications for years because of its flexibility and interoperability, resulting in millions of lines of CORBA code in today's defense systems. It can be found in defense applications ranging from command and control to weapons systems to air traffic control systems.

A CORBA application is architected as a set of communicating objects, each able to provide services or utilize the services provided by another object. The CORBA middleware handles all of the details of communication between objects. The application is unaware of where an object is physically hosted or how messages are transported among objects. All CORBA object communications are candidates for parallel execution. During a system update, parallel execution can be increased by re-deploying CORBA objects in new processes across several microprocessors or moving them to new multicore microprocessors without requiring application refactoring.

Internal tests show that applications using multicore-enabled middleware can achieve a linear increase in performance as each core is added without rewriting code.

#### How middleware affects performance

Middleware frameworks can create performance bottlenecks stemming from their design and implementation. Some of the ways that middleware can be a bottleneck include:

- Protecting critical sections

- Resource usage

- Networking

Locks are necessary to keep critical sections of the application or system resources protected from being used by more than one execution thread at a time. However, poorly designed middleware uses locks very inefficiently, for example, too many locks are created or code segments locked are too large. Efficient middleware minimizes the number of locks and ensures that each thread holds the lock for the minimum amount of time.

Middleware can also consume excess resources. For example, if the middleware opens too many file descriptors that identify system components such as communications sockets, it can consume too many resources. This causes the operating system to slow or even halt application execution. Again, efficient middleware will consume minimal resources.

A key component of middleware is the data network transport services that read and write data to the network. How well these services exploit the power of today's multicore processors plays a major role in determining an application's performance.

Issues to consider include the speed of each transport and whether the middleware can support concurrent processing across a network interface. It is also important to determine if middleware can use different physical network transports such as PCI, FireWire, shared memory, TCP/IP, RapidIO, ATM, and InfiniBand. A well-designed middleware will include a pluggable transport architecture that places no limit on the number or types of transport that can be used.

#### Multicore performance simplified with efficient middleware

As critical as the middleware communication framework is, it is often overlooked as an opportunity for improving application performance. Most legacy middleware is unable to take full advantage of today's multicore processors and can hobble application performance despite careful upgrades to other portions of the application infrastructure. Replacing legacy middleware implementation with multicore-capable middleware, such as the ORBexpress, is a low-cost, low-risk option that can simplify system architecture, enable reuse of legacy source code with a minimum amount of additional programming, and enable increased system performance.

Charles Rush is Senior VP of the Middleware Technologies Group at Objective Interface Systems, Inc. He can be contacted at charles.rush@ois.com.

#### Daily Briefing: News Snippets

By Sharon Hess, Assistant Managing Editor

www.mil-embedded.com/dailybriefing

#### Data must-haves: Proven reliability, fast transmission

While advanced, battlefield-savvy technology is paramount, what good is it without the ability to transmit data through it – as reliably and quickly as possible? Accordingly, Northrop Grumman continues to ensure reliability via its recent successful second flight test phase completion pertaining to the U.S. Army's Multi-Role Tactical Common Data Link (MR-TCDL) system. The 14-flight test series comprised a NASA-ER2 aircraft (Figure 1) and a Gulfstream II aircraft, both of which featured integrated MR-TCDL. The two aircraft were digitally linked together as well as to specified ground entry points. The testing outcome indicated that MR-TCDL provides data transmission - reliably – in excess of 200 Mbps between aircraft separated by more than 270 nautical miles and between ground networks and more than one aircraft. MR-TCDL additionally facilitates fast extension and connection of wireless and terrestrial wired networks. L-3 Communications Systems is MR-TCDL's builder.

Figure 1 | A NASA-ER2 aircraft was one of two aircraft participating in Northrop Grumman's recent MR-TCDL testing. Photo courtesy of NASA

#### **DARPA** contract boosts jamming capabilities

DARPA has enlisted BAE Systems National Security Solutions to incarnate "counter-adaptive wireless communication threats" technologies, per a recent \$8 million contract between the two entities. The technology will fall under the Behavioral Learning for Adaptive Electronic Warfare (BLADE) program umbrella, entailing new techniques and novel algorithms to arm DoD electronic warfare systems with the capability to automatically jam battlefield RF threats – and within appropriate time frames. Contract work will occur at BAE's Burlington, MA; Piscataway, NJ; and Nashua, NH sites and is slated for completion by May 2012.

#### Navy subs/ships ride the COTS wave

In the wake of seemingly endless defense spending cuts, the U.S. Navy's move toward suiting up or refitting its surface ship and submarine systems with open architectures is becoming reality. The evidence: A recent Phase III Small Business Innovative Research (SBIR) contract modification of \$16 million to The Consulting Network, Inc. The modification covers "required services ... related to open architecture concepts" such as hardware and software development and integration, and COTS products procurement for myriad surface ships and Virginia-class/other subs. Services and wares under the contract modification will be proffered when requested by the Navy, with the goal of readying future versions and legacy flavors of Navy systems for Global Information Grid (GIG) and FORCEnet compliance. Contract work is slated for fulfillment by this September. The contracting activity is the Naval Sea Systems Command in Washington, D.C.

#### Sensitive mil apps will claim their power

"Sensitive military electronic applications" might soon have a new life force to sustain them, according to a recent contract between the United States Air Force Research Laboratory (AFRL) and City Labs, Inc. The almost \$1 million contract specifies that City Labs incarnates long-life batteries for possible use in radar systems, UAVs or drones, computers, aircraft, and sensors (Figure 2). The City Labs battery, based on tritium, can withstand temps of -50 °C to +150 °C, along with extreme altitude and vibration. Used for illuminating Exit signs on commercial aircraft and in commercial buildings, theaters, and schools, tritium is a hydrogen-spawned radioactive isotope. Hence, batteries based on it are touted to last as long as 20 years.

Figure 2 | Radar systems are one type of "sensitive military electronic application" set to benefit from a recent contract between the AFRL and City Labs, Inc. for long-life batteries.

#### Super Hornets fly in early

Four ahead-of-delivery-schedule iterations of Boeing's F/A-18F Super Hornet multirole aircraft recently touched down on Australian soil for assimilation by the Royal Australian Airforce (RAAF) (Figure 3). This latest delivery brings the RAAF's total F/A-18F Super Hornet ownership to 15, with 9 more on order. The early delivery of the aircraft to Base Amberley facilitated RAAF's ability to achieve IOC [Initial Operating Capability] faster, as the RAAF transitions from the classic Hornet and F-111. Though all 15 F/A-18F Super Hornets delivered to the RAAF sport Raytheon's APG-79 Active Electronically Scanned Array (AESA) radar, 3 of the 4 recently delivered iterations were "prewired for potential conversion to electronic attack capability," as will be all remaining RAAF Super Hornets, Boeing reports.

Figure 3 | Boeing recently delivered four more iterations of its F/A-18F Super Hornet multirole aircraft to the Royal Australian Airforce, ahead of schedule. Photo courtesy of the Australian Department of Defence

#### Unmanned vehicle thwarts sub threats

When a system is autonomous, technicians and other military personnel are free to use their time for other pressing matters. A recent \$2 million DARPA contract with prime Science Applications International Corporation (SAIC) supports this paradigm, stipulating that SAIC develops an autonomous, unmanned surface vessel concept. Dubbed the Anti-Submarine Warfare (ASW) Continuous Trail Unmanned Vessel (ACTUV) Phase I, the unmanned vessel program's purpose is to aid in thwarting modern threat submarines. The primary goal: to produce an unmanned surface vessel that sustains ongoing, autonomous tracking of threat submarines. Potential missions include undersea warfare, enforcing "maritime rules of the road," and continuous at-sea operations. Five other companies will assist SAIC in Phase I, which spans the contract's six-month duration.

For consideration in Daily Briefings, submit your press releases at http://submit.opensystemsmedia.com. Submission does not guarantee inclusion.

Figure 4 | A recent U.S. Army/General Dynamics Land Systems contract provides for conversion of 42 Abrams M1A2 battle tanks into an M1A2S variant for the Kingdom of Saudi Arabia. Photo courtesy of U.S. Army

#### Abrams tank gets away with new configuration

The trusty Abrams M1A2 battle tank is about to undergo a metamorphosis, per a recent U.S. Army contract with General Dynamics Land Systems for \$37 million (Figure 4). Accordingly, 42 of the tanks will be re-engineered to sport a new M1A2S configuration for delivery to the Kingdom of Saudi Arabia. The M1A2S variant is reportedly equipped with additional lethalityincreasing capabilities and renders reduced obsolescence. General Dynamics is slated to fulfill work under the contract at its Lima, Ohio locale by September 2012. The contracting activity is the U.S. Army TACOM LCMC.

#### **Technology duo benefits from Navy contract**

The mention of one-half of any famous pair brings to mind the other half ... Antony and Cleopatra, Romeo and Juliet, and certainly for myriad years: MH-60R and MH-60S. Case in point (regarding the latter duo, anyway ...): A recent \$72 million contract between the U.S. Navy and Lockheed Martin Mission Systems and Sensors in Owego, NY, stipulates that Lockheed Martin will provide 24 mission avionics systems plus common cockpits for MH-60R (Figure 5). Additionally, MH-60S will benefit from the 18 common cockpits afforded by the contract. Both of the multimission, maritime helicopters' end-of-life components are also covered under the contract. The contracting activity is the Naval Air Systems Command, and work completion is anticipated by December.

Figure 5 | The oft-paired MH-60R and MH-60S maritime helicopters will benefit from a recent \$72 million contract between the U.S. Navy and Lockheed Martin. Lockheed Martin photo

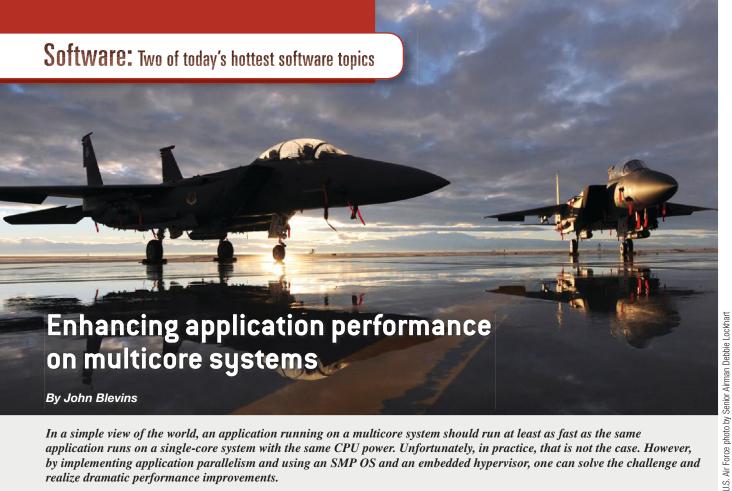

In a simple view of the world, an application running on a multicore system should run at least as fast as the same application runs on a single-core system with the same CPU power. Unfortunately, in practice, that is not the case. However, by implementing application parallelism and using an SMP OS and an embedded hypervisor, one can solve the challenge and realize dramatic performance improvements.

Let's face it. The Multicore Era is upon us. How did we get here? For years, processor manufacturers delivered on the Moore's Law promise of doubling CPU performance every couple years by increasing the number of transistors, increasing clock rates, and increasing instruction-level parallelism. We saw clock rates go from 1 GHz in the year 2000 to 2 GHz in 2001 and finally to 3 GHz in 2002, where we seem to have hit a clock-speed brick wall.

The combination of increasing power demands and rising chip temperatures seems to have put the brakes on the clock speed race. One of the surest signs was Apple's switch from the PowerPC to the Intel Architecture. Promises of 3 GHz PowerPC G5 processors in Apple laptops never materialized due to power and heat problems. Processor manufacturers quickly realized that to keep doubling performance, they needed a new trick. That new trick was to add multiple cores to a chip. Now Mac computers with 12 cores at 2.93 GHz exist, and coincidentally, dual- and quad-core single board computers and systems are very prevalent in the military embedded realm today.

However, if the software running in the system is not optimized for multicore,

there can be degradation in performance when migrating from a single-core based system. The higher transistor density in a multicore CPU does not generally translate to an increase in speed on applications that are not parallelized. Additionally, SMP OS and embedded hypervisor RTOS technologies can aid optimum performance in single-core to multicore migration. But first we will examine the issues of synchronization, concurrency, and scheduling.

#### Synchronization and concurrency overhead kill performance

A real-time embedded SMP operating system must maintain deterministic scheduling and interrupt response as well as respond rapidly to interrupts and high-priority tasks. This job becomes substantially more difficult and time consuming in a multicore CPU. For example, when multiple CPUs are active, data may be accessed by more than one of them simultaneously, adding a new level of concurrency issues for the OS to deal with. This requires additional mechanisms for concurrency control. Because of the increased concurrency in multicore systems, locking and synchronization mechanisms are more complex and take more CPU time than in singlecore systems.

Generally, on a single-core system, a critical section of code can be protected from interrupts by simply disabling preemption, doing the necessary work, and re-enabling preemption. Enabling and disabling preemption can be as simple as storing a value in a variable. In a multicore system, each core has its own unique set of interrupts, so disabling preemption does not make a lot of sense, since code on the other cores could still execute the critical section. Instead some form of locking needs to be introduced. In LynxOS, a deterministic hard real-time OS from LynuxWorks, this is done with Kernel Spinlocks and requires the use of special hardware mechanisms such as locked bus cycles. These mechanisms are considerably more complex than the simple memory accesses a single-core system uses, and this complexity adds to overall performance degradation.

In addition, when code on one core is in a critical section, code on other cores is blocked waiting for the code to finish the critical section. If the locks are coarsegrained, it is possible that several cores could be idle because they are unable to schedule any useful work.

The synchronization and concurrency overhead incurred on multicore systems

Operating systems compiled to support multiple cores are typically about 10 percent slower on a single-core system than the same operating system compiled to support a single core.

is most visible at the operating system software level, but is also apparent in multi-threaded applications that rely heavily on constructs like condition variables, semaphores, and message queues. Operating systems compiled to support multiple cores are typically about 10 percent slower on a single-core system than the same operating system compiled to support a single core.

#### Scheduling threads across multiple cores

The scheduling algorithms play a key part in harnessing the power of multiple cores and can cause performance issues if not implemented carefully. Typical scheduling algorithms maintain a per-CPU queue of threads that are ready to run and allocate CPU time based on this queue. However, in a real-time system, it is critical to preserve real-time determinism, so the scheduling approach is different. The scheduling happens on a global basis where the highest-priority thread runs on the first available CPU. However, this may lead to higher levels of cache misses. This can be addressed by using design optimizations in real-time thread scheduling.

One such design optimization, known as processor affinity, allows applications to request an "affinity" to a processor core. In this case, the operating system schedules the applications on the preferred processor core, as long as it does not affect overall system scheduling. A more rigid form of processor affinity is processor binding, where the task is always scheduled on the same processor core. However, this approach in RTOSs may lead to priority inversions. Operating system design should accommodate considerations such as processor affinity

without degrading real-time determinism and responsiveness. In the context of a real-time operating system, other key factors such as priority scheduling and interrupt latency should be preserved in multicore architectures.

An SMP-enabled real-time operating system must schedule tasks dynamically and transparently between processors to efficiently balance workloads using available processors. It optimizes the support of load balancing on multiple cores along with preserving the key elements of real-time latency and determinism. If the operating system "bounces" the application from core to core, the application will take additional Translation Lookaside Buffer (TLB) and cache misses, reducing performance. On the other hand, if the application is "pinned" to a core, there may be enough additional demand placed on that core to slow down the application, compared to running it on a single core.

#### Taking full advantage of multicore processors

To maximize multicore performance, application parallelism, SMP-enabled OSs, and embedded hypervisor technologies should be explored.

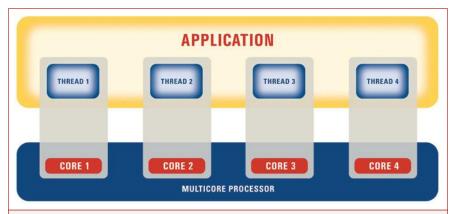

#### Application parallelism maximizes CPU utilization

All applications should be carefully examined for opportunities to parallelize the tasks. In parallel computing, an application is broken down into threads that execute independently on separate cores (Figure 1). Application parallelism is dependent on the ratio of computation to communication overhead. The computation is the amount of time the CPU spends executing application code. The

communication overhead is the amount of time that the OS spends in communicating between cores. In a typical multicore architecture, the communication overhead indicates how often messages are sent between different cores. The more threads an application has, the higher the chances that they are scheduled on different cores, which in turn increases the communication overhead.

Each type of system has different characteristics, but when optimizing application parallelism to maximize performance, there are broadly two types of application parallelism that can be used:

- 1. Coarse-grained parallelism is characterized by large tasks, single threaded and low communication overhead. In this case, the ratio of computation to communication overhead is high. This indicates that the communication overhead is lower than computation time, thereby yielding better multicore performance.

- 2. Fine-grained parallelism is characterized by small tasks, multithreaded and high communication overhead. In this case, the ratio of computation to communication overhead is low. This indicates that the communication overhead is higher than computation time, thereby yielding lower multicore performance.

Applications that are CPU-bound can exploit the full power of multicore architectures since they are coarse-grained, while memory-bound or I/O-bound applications (fine-grained) may need to be optimized to avoid the bottlenecks that arise due to the communication overhead in symmetric multiprocessing architectures.

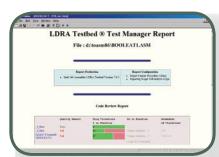

Figure 1 | In parallel computing, an application is broken down into threads that execute independently on separate cores.

POSIX-based OSs provide a rich environment of threading functionality to make it easy for developers to implement parallelism in their applications. Developers must consider the design trade-offs of using multithreading versus nonmultithreading to harness the power of multiple processor cores. In some instances, applications may perform better on a single-core system.

#### Multicore optimization with SMP OS and hypervisor technology

Another approach to multicore optimization centers around choosing an

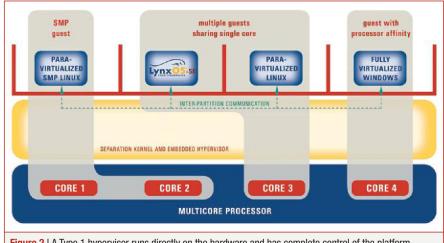

Figure 2 | A Type 1 hypervisor runs directly on the hardware and has complete control of the platform.

#### **ONE STOP SWaP**

Nallatech FPGA Solutions Reduce SWaP, Cost, and Deployment Time

#### Rapid Prototype

Start FPGA solution co-development now with Nallatech's broad range of hardware, firmware, and software.

#### Optimize Design

Nallatech increases performance and reliability while reducing component count, power consumption, and cost.

#### Miniaturize & Ruggedize

Parent company (ISI) expertise includes 3D. bare die, stacked-die modules, and custom interconnect.

#### O Deploy & Support

Extensive in-house capabilities facilitate expedited production ramps and timely post deployment support.

An Interconnect Systems, Inc. Subsidiary

Designed and Manufactured in the U.S.A. www.nallatech.com 805.383.8997 info@nallatech.com

appropriate OS. An SMP-enabled OS can help add concurrency to an application by balancing the threads running on multiple CPUs and maintaining a deterministic hard real-time performance level.

But what if you could get even more control over how the OS runs on the multicore CPU? A new trend emerging in multicore environments is the use of a small hypervisor operating system, which abstracts the capabilities of hardware and allows multiple heterogeneous operating system instances to run on a single hardware platform. A Type 1 hypervisor, such as LynxSecure from LynuxWorks (Figure 2), runs directly on the hardware and has complete control of the platform, providing superior utilization of processor resources. In the SMP-enabled hypervisor, a single copy of the hypervisor can allow a single guest operating system to utilize multiple cores. The same hypervisor can enable AMP by allocating a single guest operating system to a unique core. This can be extended to allow AMP and SMP on the same platform through judicious allocation of guest operating systems on single or multiple cores, thereby increasing processor utilization significantly.

John Blevins is the Director of Product Marketing and Tools Development at LynuxWorks, with more than 25 years of software experience in the embedded

industry. Contact him at jb@lnxw.com.

LynuxWorks 408-979-3900 www.lynuxworks.com

# Mission Critical Control the sea Cutting-edge reliability Royal Navy Astute Class nuclear-powered attack submarine.

Wind River embedded solutions deliver the breakthrough dependability and performance essential to innovation.

To control the sea, a submarine depends on remaining invisible. But when designing and building a sub, visibility is critical. That's why Thales partnered with Wind River to create a breakthrough in periscope design for the Royal Navy's new Astute-Class submarine.

Relying upon the proven innovation, reliability and performance of our VxWorks RTOS platform, Thales developed a state-of-the-art optronic imaging system that provides stable, high-resolution views in the world's most demanding conditions.

It's the kind of teamwork and support that's made Wind River a trusted leading provider of advanced embedded solutions for aerospace and defense.

To see how Wind River can help you innovate with confidence, download our Mission Critical Toolkit at www.windriver.com/missioncritical/security.

WIND RIVER

Thales' periscope provides a 360° scan of the surface above with minimal risk of detection.

® 2010 Wind River Systems, Inc. The Wind River logo is a trademark, and Wind River is a registered trademark of Wind River Systems, Inc. Other marks are the property of their respective owners. Photograph by: Jonathan Massey; © Crown Copyright/MOD, image from www.photos.mod.uk

Very specialized and often in-house designed solutions using highly proprietary hardware and software have traditionally dominated the embedded industry. The massive focus on cost reductions and the increased use of COTS products have led to lower hardware costs, but the cost of software remains high. However, if used and managed in the right way, open source software projects can help Military and Aerospace (M&A) system developers complete projects on time and within budget while improving the overall quality and stability of the resulting product.

The military embedded industry is in the middle of a massive change of implementation strategy. For many years, military programs were more or less exempt from commercial consideration. Both politicians and the public in general have set focus on the cost of military programs. Moore's law and increased use of COTS products have contributed to lower hardware cost, but software has not experienced a similar cost reduction path.

Can open source software help in getting more out of limited project budgets? According to a recently released VDC report on embedded operating systems[1], the use of Linux in embedded projects shows an annual growth rate of about 50 percent, while new projects using non-Linux operating systems show a steady state. The most interesting observation is that among the projects using Linux, about 80 percent use free public Linux distributions. However, the study also shows that this 80 percent includes the projects with the longest implementation times, indicating that the use of free software does not necessarily reduce the total project cost. Thus, open source projects must be properly planned and managed.

When the benefits of open source software are utilized, the project not only completes on time and within budget, but also results in a more robust and flexible product. The challenges and benefits of open source in M&A applications are discussed, and an application example is presented.

#### Free open source versus commercial distributions

Even though the software is open source, it does not necessarily have to be free. What are the benefits of choosing a commercial open source distribution over a free alternative? The commercial Linux providers argue for better support, an integrated tool chain, and feature enhancements. Are they right?

Support is a major concern in all projects - and the most compelling argument for choosing a commercial solution. Most organizations have experienced poor support and recognize the cost of this. Unfortunately, even for commercial alternatives, responsiveness is not always a given. It is often hard to get access to the development engineers. The best one can hope for is for the issue to be resolved

in the next official release, which can be months away. For free distributions with an active user group, support questions most often get responses immediately with initial suggestions to workarounds and fixes. Oftentimes a fix is available within hours.

The next argument is: "Commercial alternatives offer an integrated tool chain with cross-compilers, ICE, debuggers, memory management tools, and so on." This is mostly true, but the number of free alternatives increases every day, and the quality of the tools continues to improve.

The area where commercial Linux distributions have the most to offer is feature enhancements. No community-based Linux distributions offer good real-time support currently. Further, DO-178 safety certification, EAL Common Criteria, and MILS are all examples of requirements not likely to be implemented as part of a free Linux distribution. In fact, it is not even clear that any Linux distribution will ever meet these most stringent criteria. For applications targeting these standards, the commercial offerings (Linux or hard RTOS) will continue to be the best bet.

#### Challenges in open source projects

Given that the choice has been made to go for a free open source alternative, either for the operating system or the application, which challenges must one expect to encounter? How can the project be managed to have the best chances of success?

Project developers must take into account that Open Source Components (OSCs) are to be used and construct the project plan accordingly. Sufficient time must be allocated for selection, evaluation, and verification of OSC.

In his article "Mission-critical development with open source software: Lessons learned," Jeff Norris at JPL[2] describes the most critical factors to consider when designing with Open Source Software (OSS): functionality, maturity and longevity, and verification.

#### **Functionality**

The search for suitable open source components can be challenging. Projects where there is a good dialogue between the end users and the development team have the best chances of success. In many cases, an open source component has functionality close to what the end customer wants, but it is not an exact match. Either the requirements can be changed slightly or the open source community can be utilized to implement the missing features. If an acceptable match cannot be found, the alternative is to revert to inhouse design for the specific component.

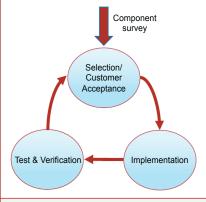

Projects using OSCs are particularly well suited for agile project management, where the project is run in small iterations, adding open source components one by one to build the required functionality. Each iteration starts with a brief analysis of the alternative components. The analysis results in selection of one component that is used to implement a few of the most critical use cases. If testing reveals that the resulting functionality does not meet the project requirements, the next iteration is started with another component. Once selected and properly evaluated, the new functionality can be presented to the customer for approval, and the process is repeated for the next component.

#### Maturity and longevity

The quality of free open source components is a concern and is often used as an argument to utilize a commercial alternative. The activity in user forums and mailing lists gives a good indication.

How well established is the open source software project? Consider how much time the development team has invested, release history, community activity, bug database, functionality backlog, and so on. Does the project have a test plan? What is the quality of the test plan? How responsive is the development team to feature requests and issue reports? Some open source communities, like SourceForge.net, assign a project ranking, which is a good indicator of the overall project activity. Look for a large and diverse development team. Watch out for single developers or small project communities. These will represent a risk when their priorities change.

#### Verification

Incorporate the open source component into the project's overall test strategy. Open source components often include detailed unit test and component-level tests far exceeding those common in commercial alternatives. These tests combined with large, active user groups constantly utilizing, testing, and verifying the code - result in overall increased system reliability. Most in-house designs do not have external review, and many do not even have internal reviews.

Open source developers know that their code will be scrutinized by a number of other community contributors. One of the main motivators for contributing is to get recognition for good and well-written code. In most cases, the result is more readable and better-documented code than what can be found in commercial

alternatives. An open source component selection checklist is imperative to the process (Table 1).

#### Application example: Ultra-small rugged NAS

A real-world example of the process described is Galleon Embedded Computing's recently announced Ultra Small Rugged NAS product. The requirements were nearly met by several open source NAS alternatives. An Intel hardware platform was chosen since most open source projects are developed for Intel Architecture. A Web search revealed a number of open source projects that were close to meeting the requirements: FreeNAS (BSD based), CryptoNAS and NASLite-M2 (Linux, commercial based), Turnkey Linux NAS, Gluster and OpenFiler (Linux, community based), to name a few. After a brief survey of the most promising alternatives, a more thorough evaluation was done of the two candidates that most closely met the requirements specification: FreeNAS and OpenFiler.

The two candidates are based on FreeBSD and Linux, respectively, and both alternatives met the specification with respect to functionality. SourceForge.net frontpage statistics for the two projects as of December 1, 2010 indicate that FreeNAS has a much bigger user group with almost 30,000 weekly downloads totaling more than 1 million downloads in 2010. This compares to 300,000 downloads for OpenFiler, which is still sufficient to satisfy the criteria of a large and diverse user community.

| Checklist                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul><li>Specification compliance</li><li>Responsiveness to feature requests</li><li>Ease of integration with existing features</li></ul>           |

| <ul><li>Community project ranking</li><li>User forum activity</li><li>Release history</li><li>Functionality backlog</li><li>Bug database</li></ul> |

| <ul><li>Size of project community</li><li>Responsiveness to issue reports</li><li>Community diversity</li></ul>                                    |

| <ul><li>Project test plan exists</li><li>Quality of test plan</li><li>Verification history</li><li>Bug database</li><li>Revision history</li></ul> |

|                                                                                                                                                    |

Reviewing the OpenFiler backlog, it became evident that few of the issues had been addressed recently, with the latest release based on a Linux core several generations old. The latest update was almost five months old at the time of review. The FreeNAS project, on the other hand, had frequent updates, a very active user forum, and good responsiveness to a few test inquiries. The many contributors have a diverse background, and the project has a good ranking with 95 percent of the 700-plus users providing "thumbs up" feedback. A review of

the negative feedback did not reveal any issues considered critical to the project.

Using an agile project process based on the aforementioned analysis, developers started the project by using FreeNAS in the first three iterations. These iterations focused on testing the file-system performance on solid-state disks, testing the network performance through four 1 Gb and two 10 GbE connections, and testing the functionality of the Web GUI. All test results showed that FreeNAS complied with the project requirements. Even so,

to ensure the best possible performance of the final product, two more iterations were conducted to test the file system and network performance of OpenFiler for comparison. The recommended component selection process is depicted in Figure 1.

Figure 1 | Component selection process diagram showing the component survey input

After reviewing the results of the performance tests for both alternatives, FreeNAS was chosen as the optimal solution for this project. Building the required functionality using in-house designed software would have taken years to complete, and would never have reached the same level of robustness and stability as the selected solution. Using FreeNAS, in less than three months the basic NAS functionality was ready, and the design team could start implementing specialized features not available in the standard distribution, such as GPS timeserver synchronization.

#### References:

- [1] www.vdcresearch.com

- [2] Jeff Norris, "Mission-critical development with open source software: Lessons learned," IEEE Software, January 2004

www.themis.com

©2010 Themis Com

openVPX)

Espen Bøch is VP Sales & Marketing at Galleon Embedded Computing. He has more than 15 years of experience including design and project and program manage-

ment at VMETRO and Curtiss-Wright Controls. He can be contacted at espen@galleonembedded.com.

**Galleon Embedded Computing** 0047 4777 3133 www.galleonembedded.com

SIGINT / Electronic Warfare

Network Attached Storage

Mission Computing

• Payload Controllers

• Sensor Management

• Data Link Processing

Network Processing

• Image Processing

• Fire Control

TIOC-300X

**TGA 300X**

3U VPX XMC/PMC Carrier Module

3U VPX 8-Port SATA/SAS RAID

Module with PMC/XMC Site

Mass Storage Drive Module

**3U VPX Graphics Processor**

with AMD E4690 GPU

SHORT LEAD TIME

prototype builds

runned systems

STATE-OF-THE-ART

· Components ready for

• 60 Days for pre-configured

· Efficient thermal management

SMALL PROGRAMS ARE OK

Outstanding shock and vibration

• Use preconfigured systems for IRAD,

prototypes, and small programs

# 2<sup>nd</sup> Generation Intel® Core i7 **Processor Solutions**

Optimized For Embedded Computing Applications.

#### X-ES 2<sup>nd</sup> Generation Intel® Core™ i7 Processor Solutions: Delivering Innovation

In 2010, Extreme Engineering Solutions, Inc. (X-ES) developed more Intel® Core™ i7 processor products based on VPX, CompactPCI, VME, CompactPCI Express, and XMC form factors than anyone in the industry. This year, X-ES has added solutions based on the 2nd generation Intel Core i7 processor. Providing products customers want, when they want them – that truly is innovation that performs.

X-ES offers an extensive product portfolio that includes commercial and ruggedized single board computers, high-performance processor modules, multipurpose I/O modules, storage, backplanes, enclosures, and fully integrated systems.

2nd generation Intel Core i7 processor solutions available in a variety of form factors. Call or visit our website today.

**Extreme Engineering Solutions**

608-833-1155 • www.x-es.com

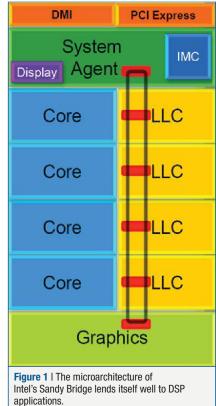

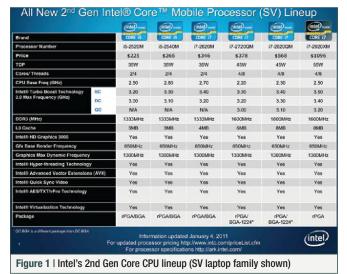

Historically, system designers have tended not to consider Intel's offering for DSP applications. With the advent of the latest architectural innovations, that seems set to change.

Military and aerospace applications have an insatiable need for processing power, but often have hard power limits. Many viable technologies exist, including DSP chips, FPGAs, and others, but in recent years developers have become accustomed to the ease of programming that comes with the use of general purpose processors, typically supplemented by integrated vector processing engines. Now, with a number of architectural features that are introduced in the latest Intel Core i7 processor products, there is a convergence of ubiquitous availability, ease of programming, and raw GFLOPS performance that makes a compelling case to consider Intel architecture chips for the most challenging signaland image-processing requirements that mil/aero has to offer.

#### Considering the road map

Traditionally, the x86 family was not particularly adept at processing streams of Floating Point (FP) data. In fact, the original Intel 8086 and successors did not have an inherent FP capability. That was left to an add-on dedicated Intel 8087 FP chip or slow software emulation. By the time the Intel Pentium processor era arrived, things had changed somewhat with the introduction of the MultiMedia eXtension (MMX technology) instructions and execution unit. This was primarily targeted at encoding and decoding various audio and video streams, but with a little ingenuity could be used for other signal-processing tasks, albeit with a limit to integer operation. Over time, MMX technology begat Intel Streaming SIMD Extensions (Intel SSE), which extended the instruction set to be ever more DSP-friendly, including floating point support.

Along the way, a non-x86 device - the Intel i860 - emerged. This was designed as a graphics device, but an embedded industry that was starved for performance discovered that it was actually pretty darn good at DSP. Unfortunately, it was a niche product for Intel when compared

with the mass markets that the x86 line served, and eventually, after a couple of generations, it fell by the wayside.

Fast-forward to late 2010/early 2011, and Intel is starting to ship the second generation of the Intel Core i7 processor line, which implements a microarchitecture codenamed "Sandy Bridge." Once again, the SIMD floating-point unit has been updated - to Intel Advanced Vector Extensions (Intel AVX) (see Sidebar 1). New architectural features and migration tools make these devices worthy of consideration for DSP applications.

#### New architectural features boost **DSP** performance

The most apparent benefit of Intel AVX is doubled vector-pipeline width. The execution unit and associated register file are both now 256 bits wide, increased from the 128 bits of previous generations. This alone can account for nearly a doubling of floating point vector performance. The execution unit uses Single Instruc-

#### Migration from AltiVec to AVX

Many developers have existing DSP code written to take advantage of the AltiVec SIMD engine on some PowerPC products. When migrating these applications to Intel SSE or AVX, there are several potential paths.

If the code was written using calls to a VSIPL library, then migration is generally simple, as companies like GE Intelligent Platforms supply VSIPL libraries for Intel SIMD. Often a recompile and link will suffice.

In cases where the code was written using AltiVec primitives called from C, using the altivec.h macros available with some compilers, Intel has worked with NA Software Ltd. to produce a macro conversion utility that can replace the AltiVec calls with Intel equivalents. Gold release code is available for download from the Intel Software Download Center.

Sidebar 1 | Once again, the SIMD floating-point unit has been updated - to Intel Advanced Vector Extensions (Intel AVX). New architectural features and migration tools make these devices worthy of consideration for DSP applications.

tion Multiple Data (SIMD) operation to increase throughput beyond what has become an effective wall in terms of what is viable by simply increasing clock rates and reducing die geometries. Clock rates above 2-3 GHz see diminishing returns for the power consumed, and as geometries migrate to 32 nm and smaller, inefficiencies resulting from leakage become more significant. A 256-bit vector pipe-

line can execute eight single precision (32-bit) FP operations concurrently (the same instruction, but on eight different sets of data points), compared with four on SSE implementations. In some cases, two instructions can be executed per cycle, such as when doing a multiply and add at the same time, thus allowing 16 operations concurrently (versus eight with SSE). In reality, each operation takes

multiple cycles, but by employing pipelining, once a startup penalty has been paid, results are available on every cycle. This SIMD operation maps naturally to many DSP algorithms as they tend to feature the required data parallelism.

There will be members of the new Intel Core i7 processor family with two and four cores featuring the Sandy Bridge architecture. Each core has its own Intel VX unit. This means that a quad-core version can potentially execute 64 single precision FP operations every clock cycle. Contrast this with the 16 operations per cycle on first-generation, dual-core i7 devices.

New instructions such as broadcasts and masked loads and stores enable better utilization of the available FLOPS. Changes to the memory unit allow for two read requests and one write of 16 bytes each in one cycle. This is a key feature in keeping the execution unit fed with data and avoiding the pipeline stalls that can severely impact performance. These features serve to close the efficiency gap that existed between AltiVec and SSE in

some DSP algorithms that required data reorganization for efficiency. Figure 1 shows some of these features.

Hence, the key elements in deploying these processors in mil/aero signal- and image-processing applications include:

- The availability of BGA devices, which allow the components to be soldered down, rather than using socketed devices that can fail under high levels of shock and vibration

- Intel's seven-year life cycle for parts on the embedded platform road map

#### Harnessing DSP application performance

So what does all this mean for performance? In an attempt to answer that question, several DSP applications have been run on previous generation i7 class devices codenamed "Arrandale" and on Sandy Bridge. When comparing performance using a single core, with both classes operating at the same clock rate, an increase in performance of approximately 2x has been demonstrated with Sandy Bridge. This illustrates both the theoretical speedup that would be expected from doubling the SIMD unit width, and

Desks/Consoles

(Mobile, Rugged, Integrated)

also the balance of memory access needed

to achieve that increase.

All this performance is great, but how can it be exploited for application domains such as radar, SIGINT, ELINT, and so on? At the lowest level and highest complexity is programming the Intel AVX unit using primitives that can be called from C or other high-level languages. While no more complex than the assembly code programming that many programmers cut their teeth on in the past, getting good performance at this level is not a trivial task. Many factors must be understood and factored in when coding to avoid pipeline stalls and resource contention.

Compilers offer some help. Several already have Intel AVX support, coupled with varying degrees of automatic vectorization. Source code is analyzed, and where possible, for-loops are mapped to Intel AVX SIMD operations. This can be a help with dusty-deck code, but in reality there are many impediments that can preclude effectiveness, as the compiler must always err on the side of caution. Where ambiguity exists over loop iterators, for instance, the compiler cannot make assumptions that it cannot verify, so it will always generate lower-performance, guaranteed-correct code.

Phone: 770-496-4000 Web: www.optimaeps.com

Email: sales@optimaeps.com

**Applications**

Come to the rugged design experts for a solution tailored to your

needs. Leverage our modular platforms to customize guickly

and cost-effectively. With base models meeting MIL-STD-810F,

901D, 461D, and 167, Optima has a solution for you.

Optima EF

Math libraries offer a good alternative. Intel Integrated Performance Primitives (Intel IPP) and Intel Math Kernel Library (Intel MKL) are highly tuned for Intel AVX. Algorithm coverage is broad, and performance is hard to beat. However, in some eyes, they suffer from being seen as proprietary Application Programming Interfaces (APIs). Also, support for operating systems tends to stick with the mainstream of Windows and Linux. Support for real-time operating systems common in the embedded world is currently lacking, for the most part.